嵌入式Linux裸機開發(六)――S5PV210時鐘系統

一、時鐘系統簡介

外設工作需要一定頻率的時鐘,這些時鐘都由系統時鐘提供。系統時鐘一般由外部低頻24MHZ晶體振蕩器通過鎖相環電路PLL倍頻產生。通過外部的低頻晶體振蕩器產生系統時鐘不僅可以減少干擾還可以降低成本。外設的工作頻率越高,功耗越高,越不穩定。通過關閉外設的時鐘可以關閉外設。

二、時鐘域

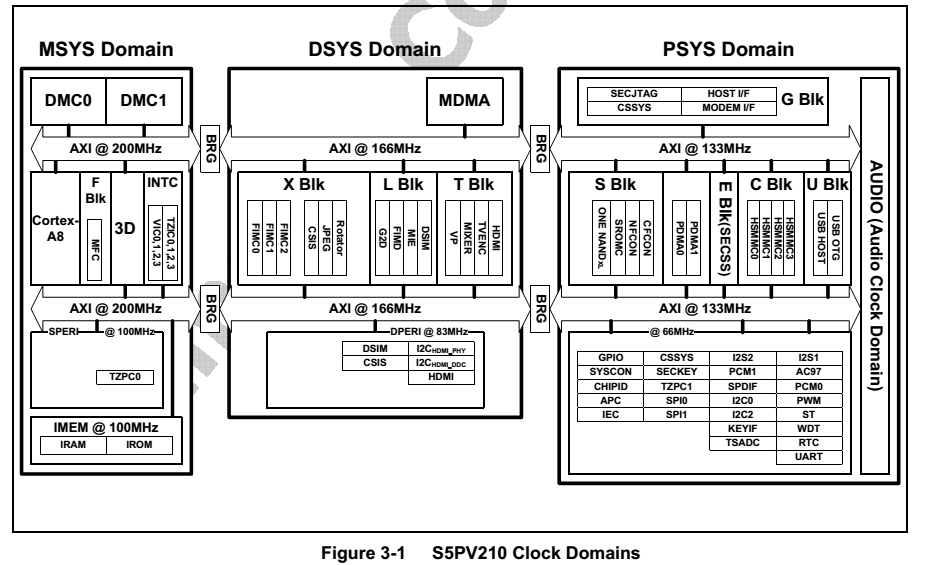

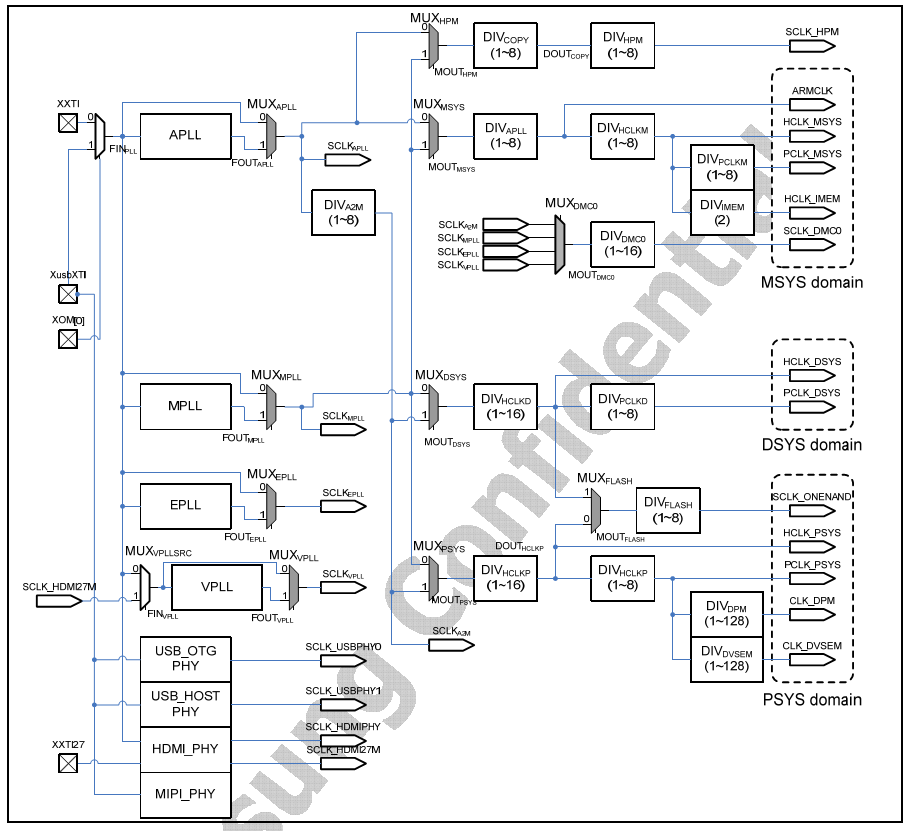

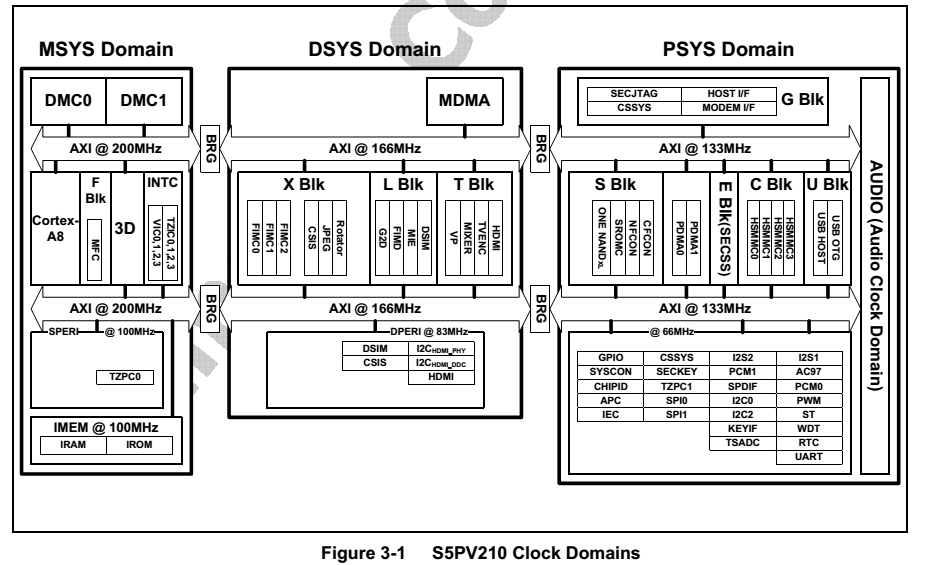

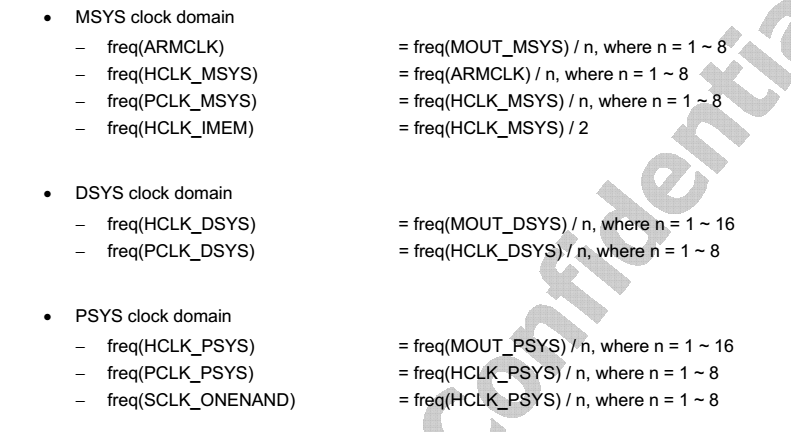

S5PV210 中包含 3 大類時鐘 domain, 分別是主系統時鐘 domain (簡稱 MSYS)、顯示相關的時鐘 domain (DSYS)、 外圍設備的時鐘 domain (PSYS)。

1、MSYS: 用來給 cortex a8 處理器, dram 控制器, 3D, IRAM, IROM,中斷控制器等提供時鐘,cortex a8只支持同步模式,因此必須用200MHZ的AXI總線提供同步。2、DSYS: 用來給顯示相關的部件提供時鐘,包括 FIMC, FIMD, JPEG, and multimedia IPs 3、PSYS:用來給外圍設備提供時鐘,如 i2s, spi,i2c,uart 等4、每一種總線系統分別提供200MHZ、166MHZ、133MHZ時鐘,兩個不同時鐘域通過異步總線橋(BRG)連接。S5PV210時鐘域圖如下:

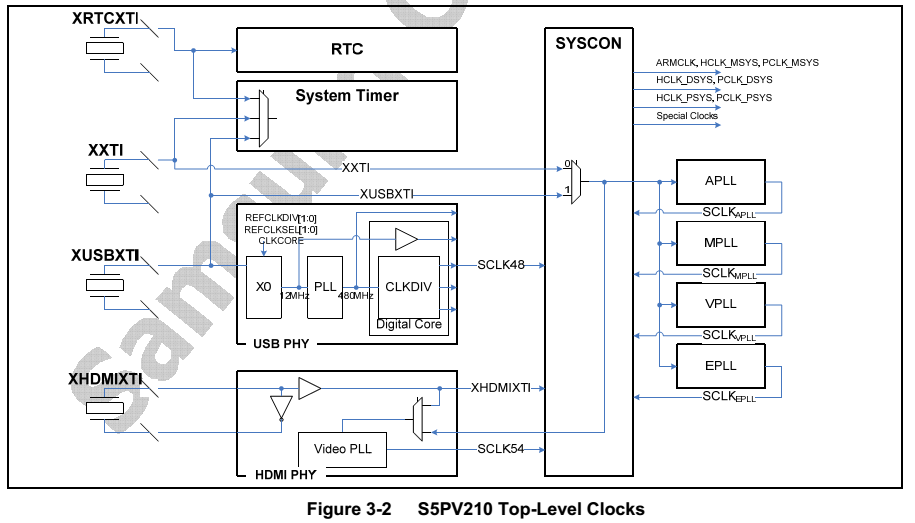

S5PV210原始時鐘來源:

S5PV210有四個外部晶體振蕩器接口,開發板設計時可以選擇外接什麼晶體振蕩器。

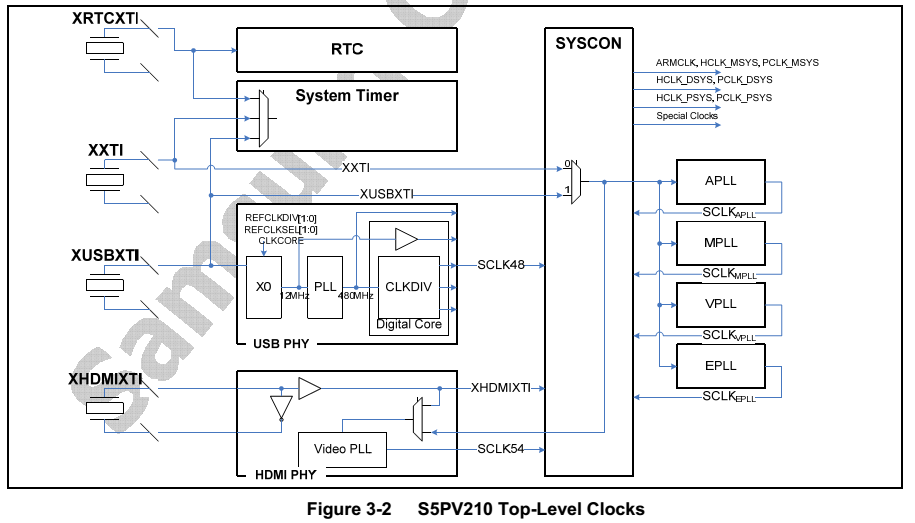

原始時鐘產生如下圖:

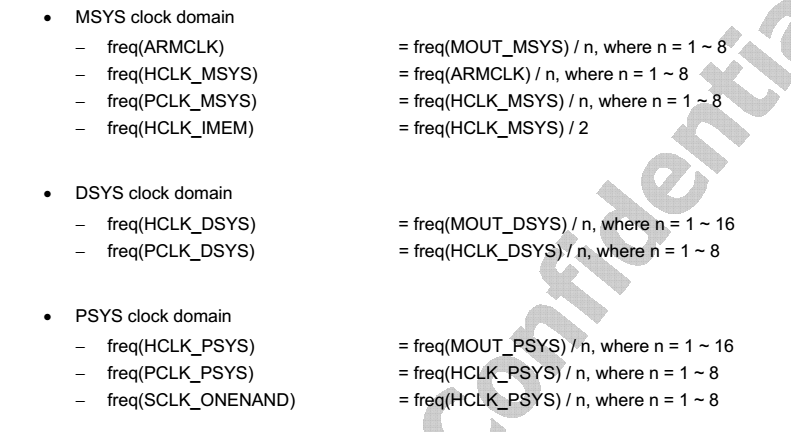

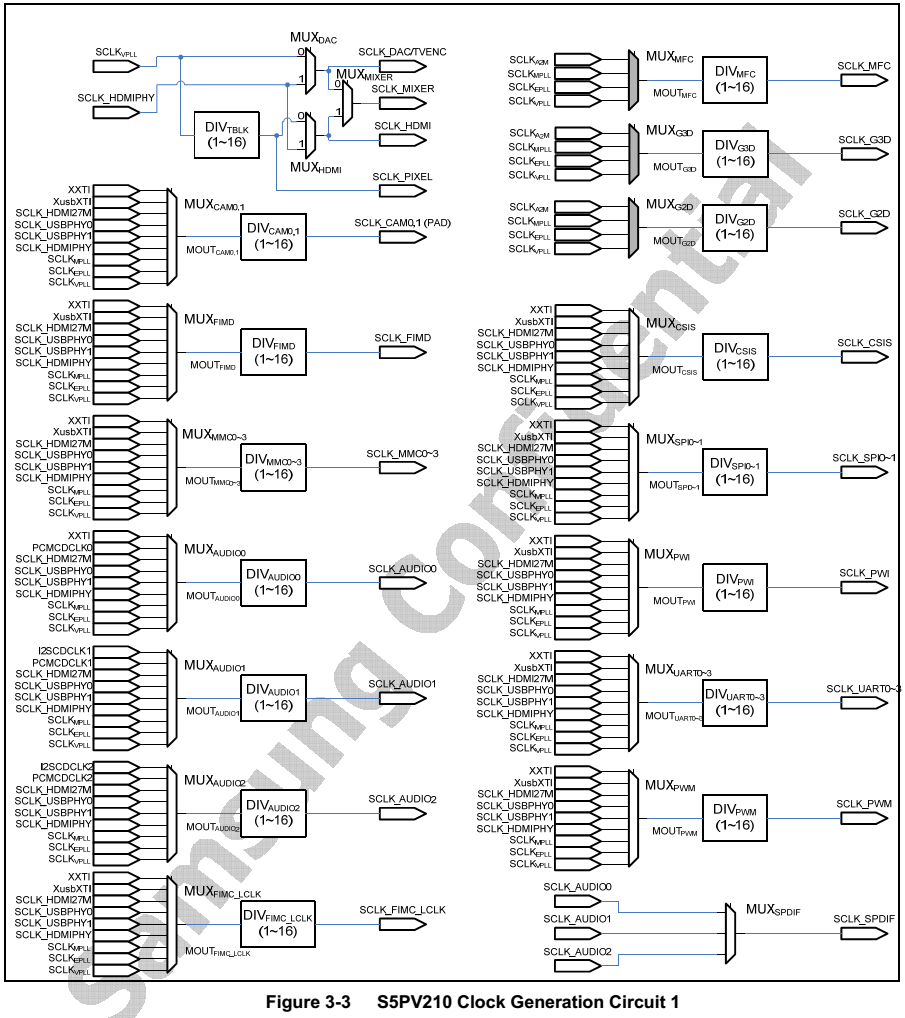

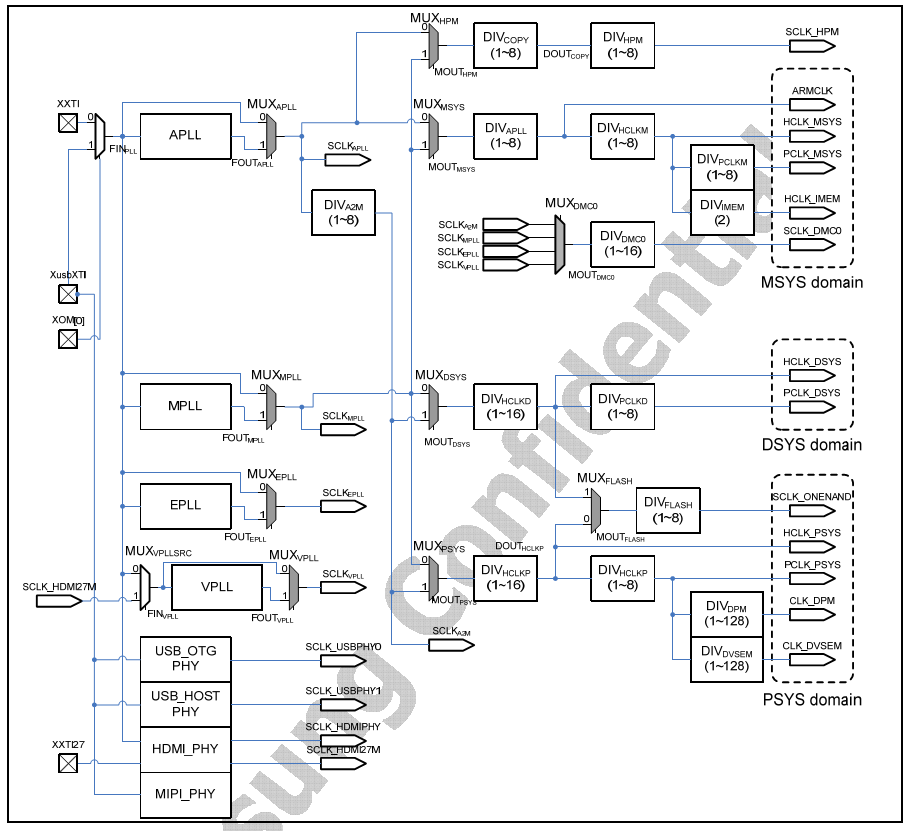

Smart210外接的晶振頻率(簡稱 Fin)為 24MHz,通過鎖相環電路PLL倍頻提高系統時鐘頻率。 S5PV210 共有 4 個倍頻器,即 PLL, 包括 APLL(供 MSYS 使用),MPLL(供 DSYS 使用),EPLL(供 PSYS 使用),VPLL(供 video 相關的時鐘使用)。 3 大類時鐘 domain中,可以使用不同的分頻,使其給不同部件輸出所需要的時鐘,各類時鐘的關系如下圖:

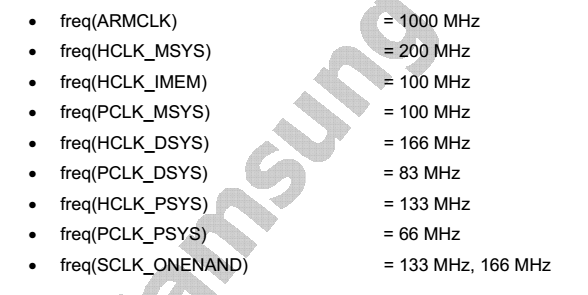

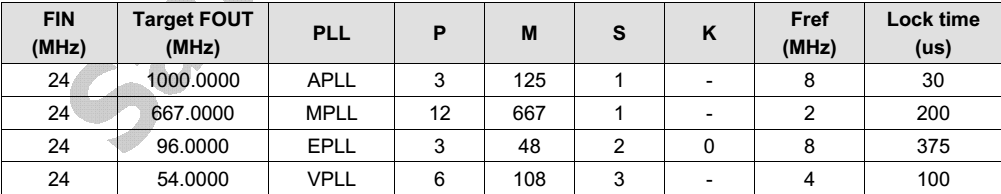

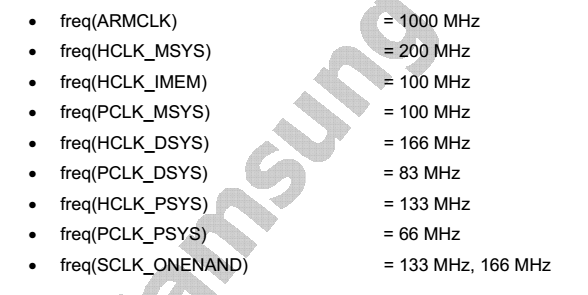

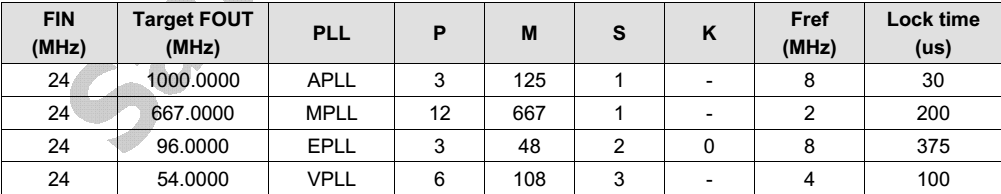

三星S5PV210推薦的時鐘設置參考值如下:

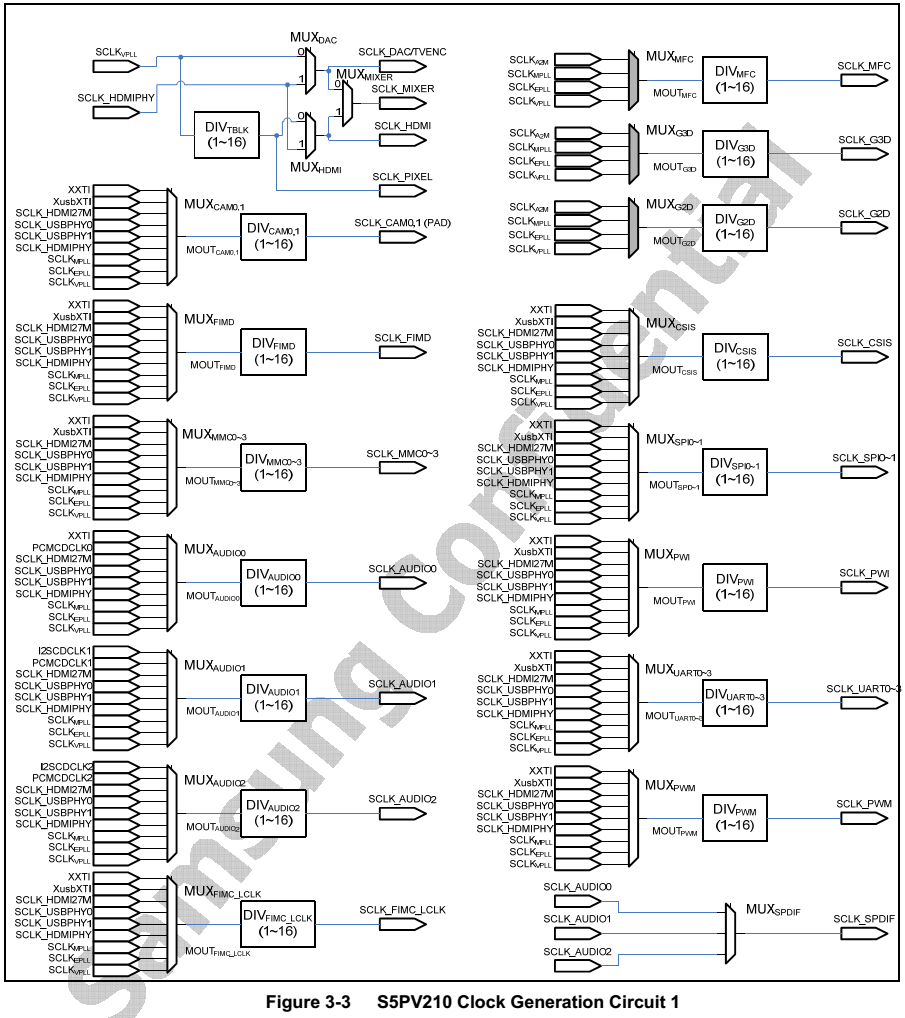

時鐘產生原理圖:

三、時鐘控制寄存器

XPLL_LOCK:控制PLL鎖定周期

XPLL_CON:打開、關閉PLL電路,設置倍頻參數

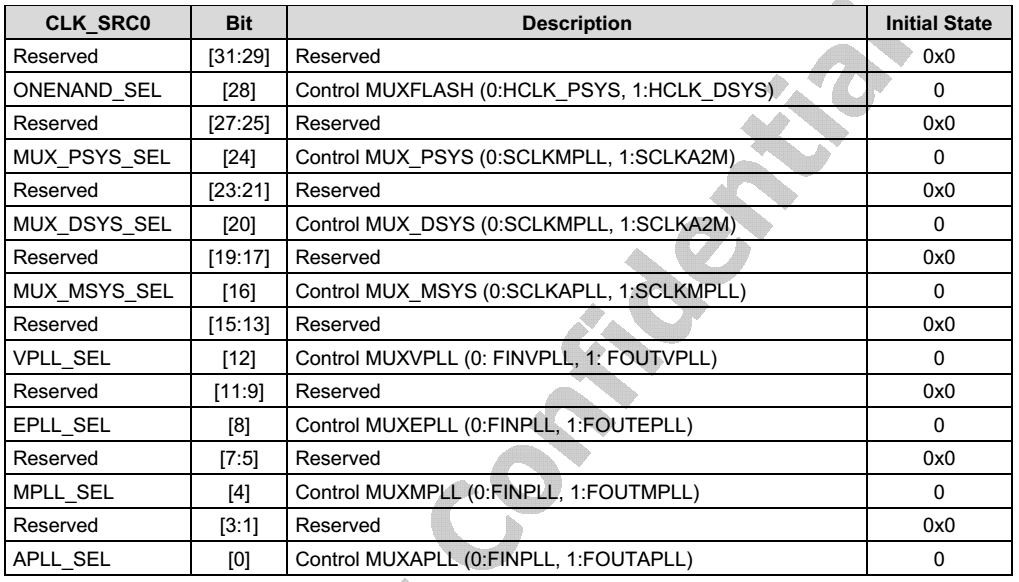

CLK_SRCX:設置時鐘源

CLK_SRC_MASX:時鐘源選擇通道設置,默認打開

CLK_DIVX:分頻器參數設置

CLK_GATE_XXX:時鐘控制

CLK_DIV_STATX:查看分頻器狀態

CLK_MUX_STATX:查看mux狀態

四、時鐘設置

時鐘設置流程:1、設置各種時鐘開關,暫時關閉PLL2、設置APLL/MPLL/EPLL/EPLL鎖相環時間

三星推薦0x00000FFF,設置最大值0x0000FFFF

3、設置PLL倍頻參數

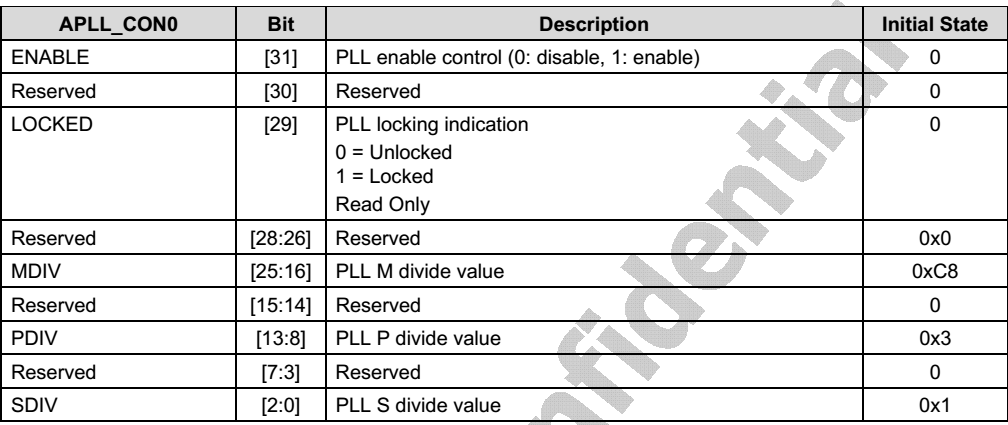

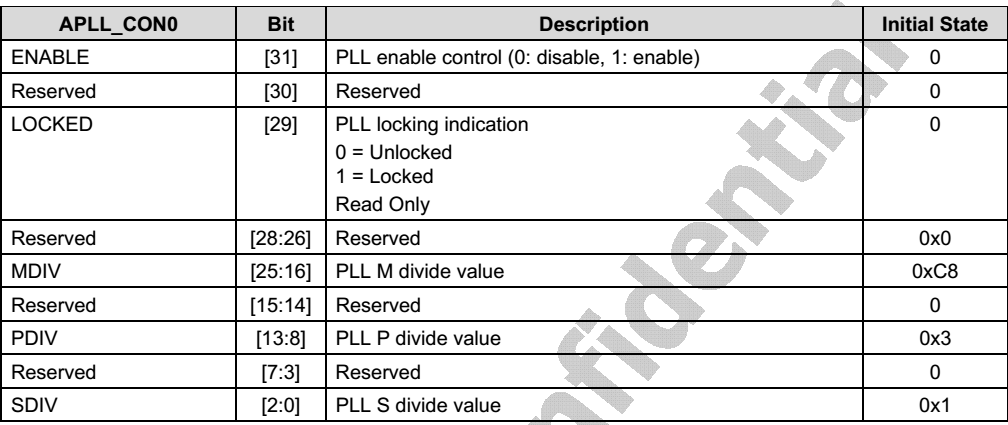

設置APLL_CON寄存器設置如下:

FOUT = MDIV X FIN / (PDIV × 2^(SDIV-1))

MPLL、EPLL、VPLL類似

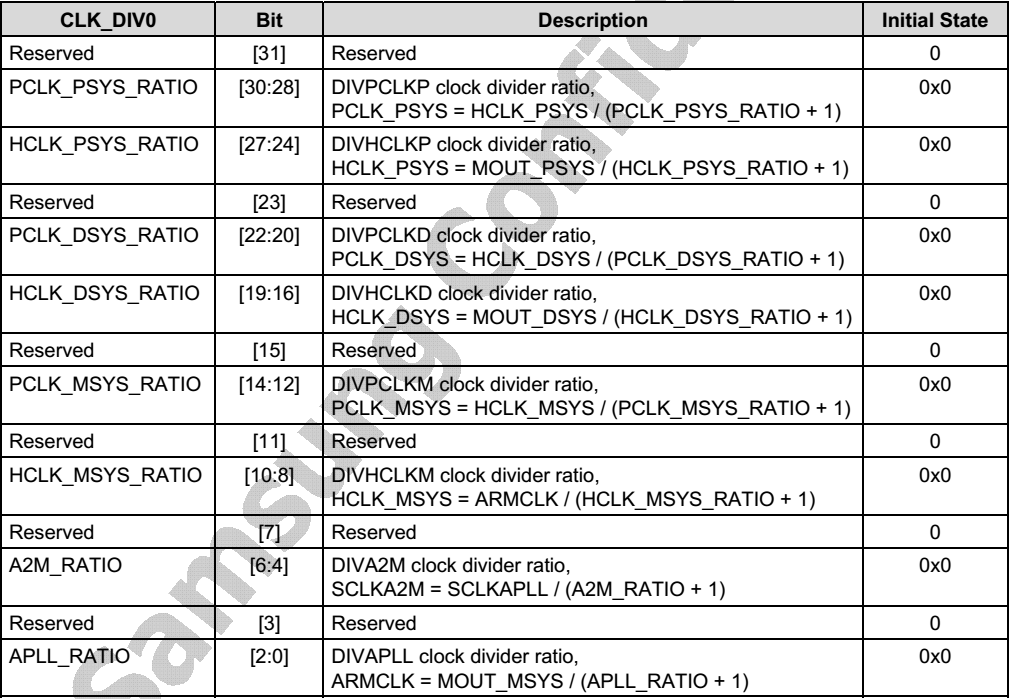

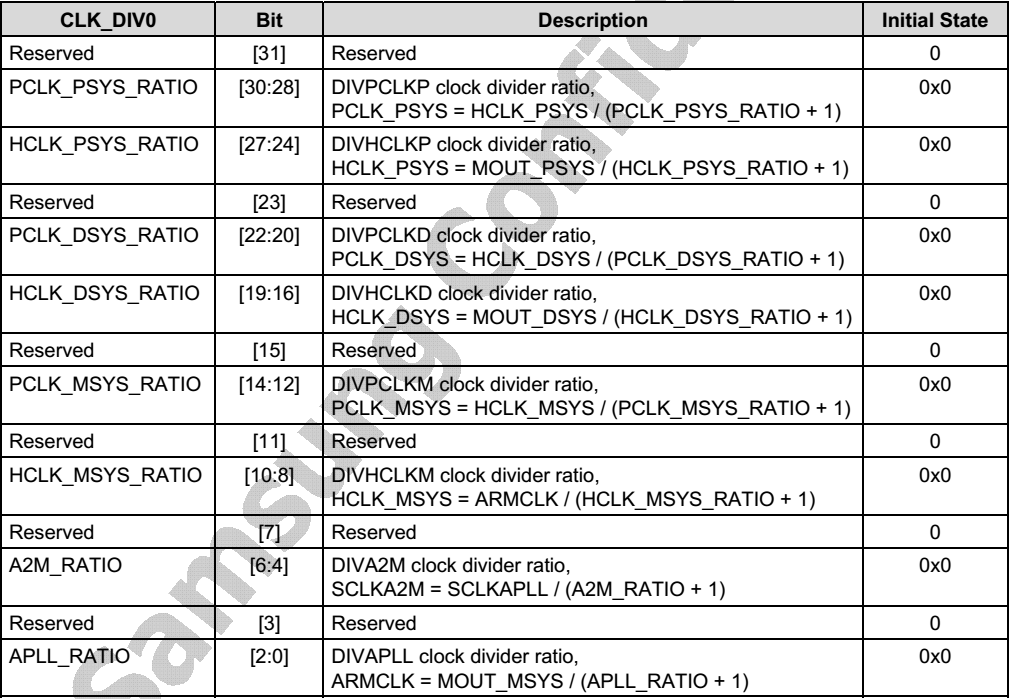

4、設置分頻參數

設置CLK_DIV0寄存器

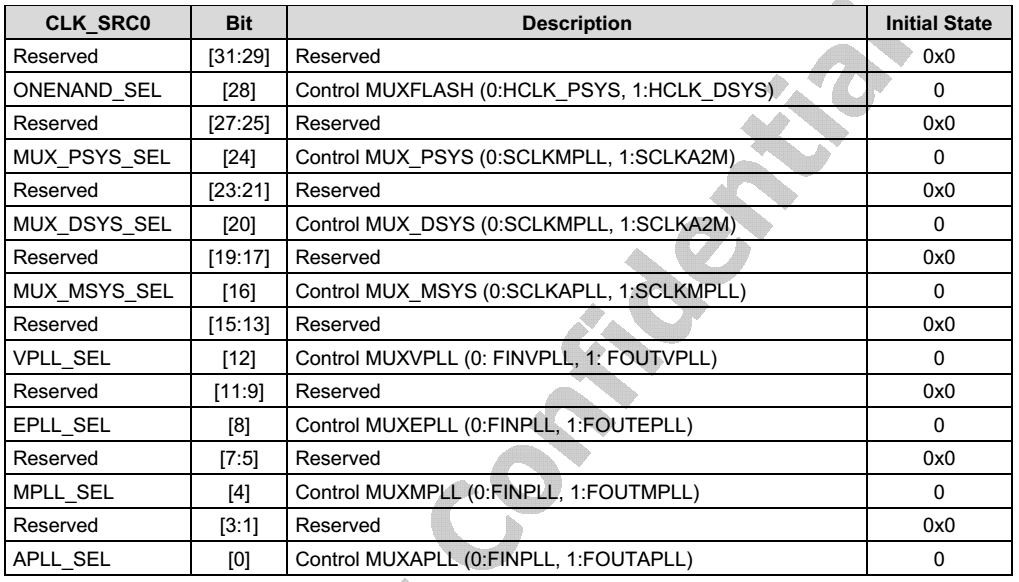

5、選擇各種時鐘源,打開PLL

結合時鐘產生的原理圖,設置CLK_SRC0寄存器

clock_init源碼:

// 時鐘控制器基地址

#define ELFIN_CLOCK_POWER_BASE 0xE0100000

// 時鐘相關的寄存器相對時鐘控制器基地址的偏移值

#define APLL_LOCK_OFFSET 0x00

#define MPLL_LOCK_OFFSET 0x08

#define APLL_CON0_OFFSET 0x100

#define APLL_CON1_OFFSET 0x104

#define MPLL_CON_OFFSET 0x108

#define CLK_SRC0_OFFSET 0x200

#define CLK_SRC1_OFFSET 0x204

#define CLK_SRC2_OFFSET 0x208

#define CLK_SRC3_OFFSET 0x20c

#define CLK_SRC4_OFFSET 0x210

#define CLK_SRC5_OFFSET 0x214

#define CLK_SRC6_OFFSET 0x218

#define CLK_SRC_MASK0_OFFSET 0x280

#define CLK_SRC_MASK1_OFFSET 0x284

#define CLK_DIV0_OFFSET 0x300

#define CLK_DIV1_OFFSET 0x304

#define CLK_DIV2_OFFSET 0x308

#define CLK_DIV3_OFFSET 0x30c

#define CLK_DIV4_OFFSET 0x310

#define CLK_DIV5_OFFSET 0x314

#define CLK_DIV6_OFFSET 0x318

#define CLK_DIV7_OFFSET 0x31c

#define CLK_DIV0_MASK 0x7fffffff

#define APLL_MDIV 0x7d

#define APLL_PDIV 0x3

#define APLL_SDIV 0x1

#define MPLL_MDIV 0x29b

#define MPLL_PDIV 0xc

#define MPLL_SDIV 0x1

#define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv)

#define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV)

#define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV)

.global clock_init

clock_init:

ldr r0, =ELFIN_CLOCK_POWER_BASE

// 1 設置各種時鐘開關,暫時不使用PLL

ldr r1, =0x0

// 芯片手冊P378 寄存器CLK_SRC:Select clock source 0 (Main)

str r1, [r0, #CLK_SRC0_OFFSET]

// 2 設置鎖定時間,使用默認值即可

// 設置PLL後,時鐘從Fin提升到目標頻率時,需要一定的時間,即鎖定時間

ldr r1,=0x0000FFFF

str r1,[r0, #APLL_LOCK_OFFSET]

str r1, [r0, #MPLL_LOCK_OFFSET]

// 3 設置PLL

// FOUT = MDIV*FIN/(PDIV*2^(SDIV-1))=0x7d*24/(0x3*2^(1-1))=1000 MHz

ldr r1, =APLL_VAL

str r1, [r0, #APLL_CON0_OFFSET]

// FOUT = MDIV*FIN/(PDIV*2^SDIV)=0x29b*24/(0xc*2^1)= 667 MHz

ldr r1, =MPLL_VAL

str r1, [r0, #MPLL_CON_OFFSET]

// 4 設置分頻

// 清bit[0~31]

ldr r1, [r0, #CLK_DIV0_OFFSET]

ldr r2, =CLK_DIV0_MASK

bic r1, r1, r2

ldr r2, =0x14131440//對照CLK_DIV0寄存器分析

orr r1, r1, r2

str r1, [r0, #CLK_DIV0_OFFSET]

// 5 設置各種時鐘開關,使用PLL

ldr r1, [r0, #CLK_SRC0_OFFSET]

ldr r2, =0x10001111

orr r1, r1, r2

str r1, [r0, #CLK_SRC0_OFFSET]

mov pc, lr

本文出自 “生命不息,奮斗不止” 博客,請務必保留此出處http://9291927.blog.51cto.com/9281927/1786916