比如取指周期的安排節拍動作

C1MAR <- (PC), R <- 1

C2MDR <- M(MAR)

C3PC <- (PC)+1

C4IR <- (MDR), CU <-OP(IR)

節拍是時序的控制信號,所有的動作都在時序的嚴格控制下

C1節拍,PC的內容也就是下一條指令的地址送入MAR中,並置讀信號為1有效 C2節拍按照MAR的地址指示從主存中讀取數據到MDR中,讀取的是一條指令 C3節拍PC自加1,指向下一條指令 C4節拍講MDR的指令送入IR指令寄存器,並將IR指令的操作碼部分送入CU控制器准備譯碼 每一個“MAR <- (PC)”的小動作就由一個微指令來完成,只涉及少數幾個部件。都是通過電信號來控制,那麼按我的猜想,給PC的輸出打開,給MAR的輸入打開,電流自然流通,PC的內容也就傳送到MAR中去了。不知道對不對,反正有電路控制下都可以實現。

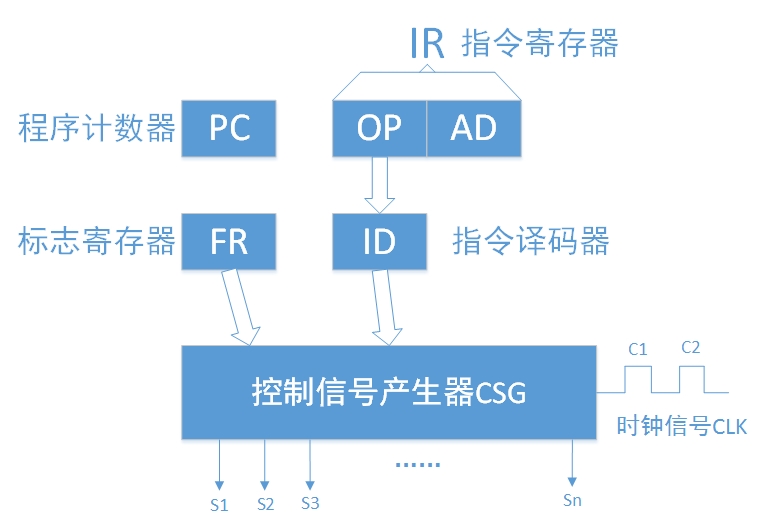

組成與功能

處理器的工作就是在控制器CU的指揮下,按照“取指令 - 分析指令 - 根據尋址方式計算操作數地址- 取源操作數 - 處理源操作數 - 寫目的操作數”的順序,周而復始地解釋指令。 CU的功能就是,對指令進行分析(譯碼),按照一定時序,根據當前處理器狀態,向計算機的各個部件發出控制信號/命令。

時序系統

操作有序的基礎,即在時序的控制下。

簡單來講就是規定時間間隔,每個時間段內完成能完成的任務,完不成就分配兩個時間段等等,但時間總是時間段的整數倍。

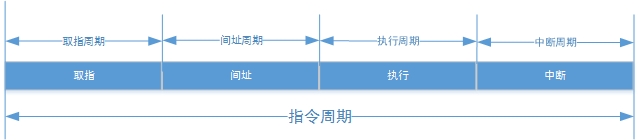

指令周期:處理器從主存取出一條指令並執行完該指令所需的時間

然而不同指令所需的時間不同,且同一指令的時間也受環境的影響,為了簡化控制,一般都設計成節拍的某個整數倍——基准周期 基准周期稱為機器周期或CPU周期,其長短取決於指令的基本操作和期間的工作速度 對於單周期處理器,所有指令的指令周期都是相同的,都等於一個機器周期。

為了保證適配所有的指令,所以指令周期就要選取最復雜指令所用的時間 多周期處理器,把一條指令的周期分為好幾個部分來細化,最簡單的兩周期就分為“取指周期”和“執行周期”

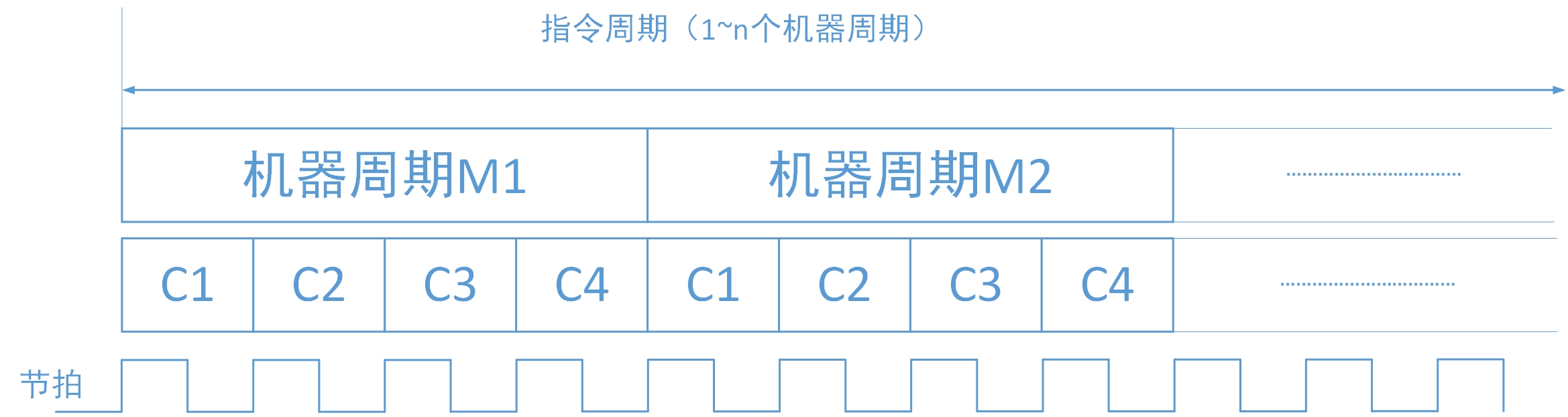

多個周期之間總得有個基准,這個基准就是機器周期 為了保證一個機器周期內至少可以完成一個指令的基本操作(細化後的一個部分),一般選取花費時間較長的一次訪存的時間(訪存依賴於總線,所以一次訪存的時間也叫總線周期) 一個標准的、同步總線的總線周期為4個節拍

三級時序

節拍

時鐘脈沖,由一個頻率相當精確和穩定的脈沖信號發生器按一定電壓幅度,一定時間間隔連續發出的脈沖信號。其頻率在CPU設計的時候就確定下來,作為最基礎的時序控制。 機器周期

CPU的基准時間,設計的長度可以保證至少能完成一個指令的基本操作,簡化了控制。 設計成節拍的某個整數倍 一個標准的、同步總線的機器周期為4個節拍

指令周期

一條指令執行所需要的時間 分為單周期處理器和多周期處理器

單周期:所有指令的指令周期一樣長。既然一樣長就干脆設置成為一個機器周期的長度好了,更簡化了控制。只不過這個時候機器周期是不是一般而言的4個節拍,那就不好說了。萬一某條指令非常復雜需要的時間超過了4個節拍呢?那就得機器周期了呗,至少得大於等於最復雜指令的執行時間吧。 多周期:指令被分為好幾個部分執行,每個部分需要的時間規定為一個機器周期,這樣機器周期才是設計為保證至少完成一個基本操作。 指令周期的例子

三級時序系統

即最底層的節拍、節拍之上作為基准的基准周期(也叫機器周期,一般設置和總線周期相同,但和總線周期不是一個概念)、再在這個基准之上在組間我們的指令周期

控制方式

一般都是多周期處理器。單周期雖然設計簡單,但太浪費了。好好的CPU時間大部分都閒著 但是多周期的話,就要考慮不同的指令其指令周期必然不同,而對指令劃分的每個部分,其也不一定會相同

雖然我們用一次訪存的時間來作為機器周期,目的是為了保證在一個機器周期內能完成一個基本操作,比如取指、間址、執行、中斷查詢這四個部分的話,就要保證一個機器周期內能完成一個部分的操作 但是對於復雜的運算,比如乘法、除法,其執行周期很可能就大於一次訪存的時間,也就是在一個機器周期內完成不了執行周期所需的完成的操作 這就尴尬了 所以我們需要控制

同步控制:和單周期處理器的思想差不多,既然把指令劃分了,那就以最長的一個部分的操作時間作為基准

假設乘除最長且需要在兩個機器周期內完成,那麼對於取指、間址等其他部分,也分配兩個機器周期的時間 但是對於大部分的操作,兩個機器周期太長了,這就會導致CPU經常處於空閒的狀態。浪費浪費 作為一種在同步控制之下的彌補手段,人們又設計了不等長的機器周期。簡單的操作就采用3個節拍的機器周期,復雜的操作采用5個節拍的機器周期。不過在此之上由需要一層控制在分配機器周期 異步控制

即采用“握手/應答”的方式來確定機器周期的長短。當進入一個機器周期的時候,將相應的某個“指令執行階段標志”置為1,當最後一個微操作結束的時候,向控制器發出一個信號,控制器再發出一個信號來將“指令執行階段標志”置為0。這樣才算一個機器周期結束 如此一來機器周期的長短也無法實現規定 聯合控制

兩種辦法相結合呗 比如在部件(如ALU)的內部采用同步,部件之間采用異步 在比如,固定機器周期的長度,但是根據指令復雜度的不同,每個指令分配的機器周期的數量也不等。這屬於聯合控制,異步中有同步(機器周期固定長度),同步中有異步(不同指令周期有不同數量的機器周期)

硬布線與微程序

終於到了微指令的部分了。 說,一條指令被控制器翻譯成多條微指令(亦稱微操作,不過微指令的“指令”層面的概念尤其對應微程序,因為硬布線實在牽扯不到“指令”層面上),而一條指令本身又是可劃分的,可以被劃分為多個部分,那麼每個部分同樣對應著多條微指令

硬布線

原理

把每個微操作所對應的需要用到的部件、信號都用邏輯電路連接起來,等合適的信號來了就自動啟動了對應了部件(通上電…開關打開…之類的)…

比如對於取指周期,一般給安排一個機器周期的時間就夠用,通常的機器周期是4個節拍,也就是4個節拍要完成取指這個操作

節拍動作

C1MAR <- (PC), R <- 1

C2MDR <- M(MAR)

C3PC <- (PC)+1

C4IR <- (MDR), CU <-OP(IR)

對於每個微操作,列出其所在的指令的哪個周期、哪個節拍、哪些指令需要用到周期節拍微指令SHLLDAMSTAMJMP XJZ XADD MCOM

FEC1MAR <- (PC)1111111

FEC1R <- 11111111

FEC2MDR <- M(MAR)1111111

FEC3PC <- (PC)+11111111

FEC4IR <- (MDR)1111111

FEC4CU <- OP(IR)1111111

EXEC1MAR <-AD(IR)0100010

…………………………

EXEC2MDR <- M(MAR)0100010

…………………………

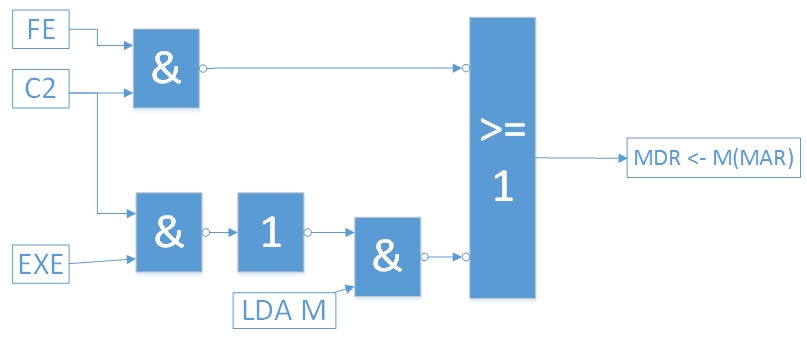

太長我就不寫了 以“MDR<-M(MAR)”為例,也就是一次讀取主存內容的微操作

從表格可以看出,在取指周期FE的C2節拍安排了這個微操作,在執行周期EXE的C2節拍也有這個操作 因為取指周期必然的(所有的指令都用到了),就是說只要到了取指周期的C2節拍,那麼這個微操作就必然要啟動執行 執行周期不一樣,有些指令需要從主存取數、而有些指令則不需要,但只要需要,就安排在了C2節拍裡。也就是說,到了執行周期的C2節拍,如果是需要從主存取數的指令,那麼這個微操作也會被啟動執行 所以對於所有的微操作,都是提前安排好了,你你你在哪個周期哪個節拍,他又在哪個周期的哪個節拍,從指令轉換成微操作序列,也需要符合這個表格所規定的微操作的先後順序

只不過這裡使用最簡單的兩周期來舉例 在設計組合電路之前,還要寫出微操作所對應的邏輯表達式

如“MDR<-M(MAR)” FE · C2 · (SHL + LDA M + STA M + JMP X + JZ X + COM) + EXE · C2 · (LDA M) = FE · C2 + EXE · C2 · (LDA M) = C2 · [ FE + EXE · ( LDA M ) ] 注:邏輯加和邏輯乘

FE、C2均是當前的狀態信號,現在是哪個周期、哪個節拍 對於LDA M信號,那自然就是ID指令譯碼器所要發出的信號了,就是判斷當前的指令是哪條指令 這個時候的輸出還只是我要啟動“MDR<-M(MAR)”這個微操作,相當於把當前指令根據時序翻譯成了微操作序列 然後這條輸出就對應到了相應的控制信號,同樣也是通過邏輯電路來對應的。

按我的理(猜)解(想),每個微操作對應多個部件,那麼要實現這個微操作就需要對每個對應的部件就要發出一個控制信號,這個控制信號被稱為微命令。差不多是很底層的命令了。不過應該還可以被相應的部件繼續翻譯(應該是吧),比如發給ALU的信號就是要告訴它進行什麼運算,是加還是減還是移位等等,ALU收到信號翻譯後聽懂了就進行相應的動作。

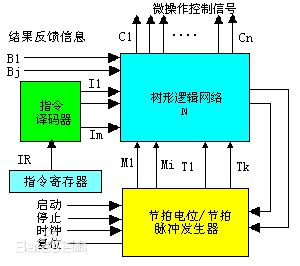

從百度百科盜圖一張

微程序

原理

既然每條微指令需要發出的控制信號都是相同的,那麼就存儲下來,用到的時候直接拿出來用不就可以了嘛。機智! 相比於硬布線,其硬件的復雜度大大降低了,只不過還需要從存微指令的地方取出來,所以花費的時間肯定要比直接采用邏輯電路的硬布線要慢 對於RISC還是采取硬布線的方式比較合算,因為RISC本身的指令就不多,硬件復雜度也不會高到哪去 歷史

其實早在1951年這個想法就被英國劍橋大學的計算機教授Wilkes提出來了,所以“微程序控制”也被稱為“Wilkes模型” 然而,當時的存儲器太慢太慢了,,,,,,,,,,,, 設計

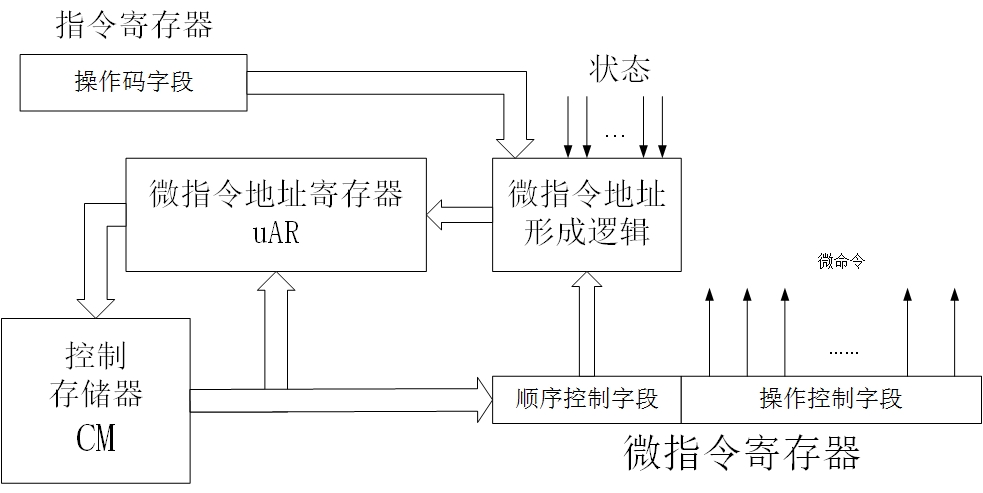

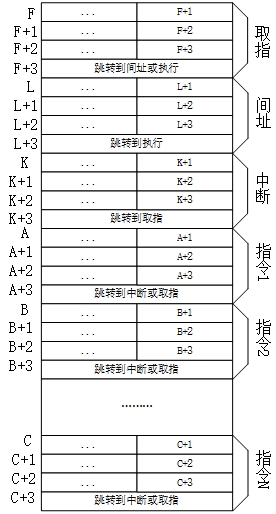

同樣是先根據周期、節拍來規定好每個微指令在何時才能執行 把微指令編制成微程序 把所有的微程序存入控制器內部的一個ROM——控制存儲器CM(Control Memory,簡稱控存) 機器運行的時候,控制器根據當前指令、狀態(節拍)取出對應的微指令,按照規定好的節拍一條一條送入控存數據寄存器CMDR 由CMDR發出微命令(即控制信號)來通知相應的部件開始干活

微程序控制器組成

原本控制器的IR、PC依舊保存,其余的見上圖 微地址形成邏輯代替了實現了指令譯碼器的功能 微指令寄存器存放當前的微指令 控制存儲器存儲所有的微指令,以微程序的形式 微指令地址寄存器(uAR)存放微指令的地址,也稱為CMAR 微程序和微指令

微程序

通常微程序可以完成一個基礎操作,比如取指操作可以編制成一個微程序。而想這種公共操作可以只存儲一份,基本上就是取指、間址、中斷判斷這三個公共的部分 對於其他每個指令,其執行部分的微指令必然是不同的,每條指令就需要對應一個執行部分的微程序 一般來說,N條指令,就需要編制N+3個微程序 微指令

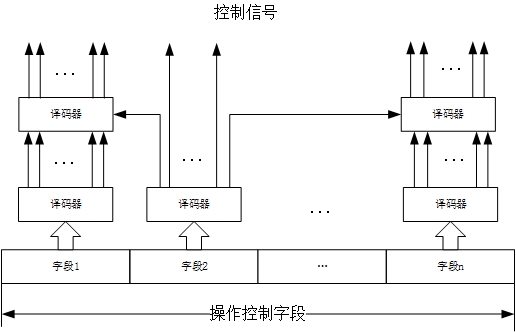

由“操作控制字段”和“順序控制字段”組成 “操作控制字段”記錄著所需要發出的微命令,因為是提前編制好的,這些微命令就可以完成這條微指令的操作 “順序控制字段”用來確定下一條微指令的地址,如果當前的微程序沒有執行完,一般就是順序加1指向下一條微指令。如果執行完了,則相當於告訴微地址形成邏輯,我當前的微程序執行完了,應該選擇下一個微程序執行了。一般是通過設置相應的標志位。於是就根據當前的指令操作碼、時序來確定下一個微程序是哪個。取指的微程序執行完了,如果當前指令需要間址則跳到間址的微程序,不需要就直接跳到當前指令的執行部分的微程序

細說微指令

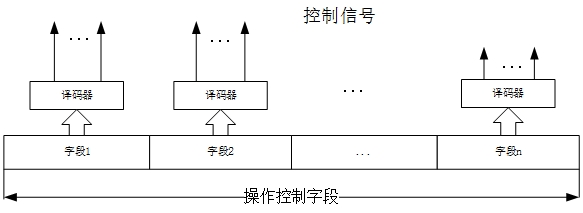

操作控制字段:記錄要發出的控制信號,有不同的編碼方式

直接表示法

每一位對應一個控制信號,如果該位為1則表示要發出這個控制信號,為0不發出 但是控制信號太他媽多了啊。輕輕松松上百個。一條指令都捨不得占幾位,一個微指令就要占幾百位。No Way! 編碼表示法

所以就編碼表示了呗 但是只有互斥(不能同時發出)的控制信號才可以被編碼 有編碼自然也有譯碼 字段直接編碼

字段間接編碼

順序控制字段

也叫“下地址” 並不是所有時候都需要用到該微指令的下地址

開機後,第一條微指令的地址由專門的電路生成 某條指令的最後一條微指令結束,那麼下一條必然為取指周期的微程序,也有專門的電路生成 一般由取指周期微程序的最後一條微指令來置“間址標志IND”為1,表示下一步要進入該指令的間址周期,由於間址是公共操作,所以也有專門的電路生成 若有條微指令置了“執行標志EXE”為1,表示要進入執行周期,則下地址由微地址形成邏輯根據指令操作碼形成。由於存儲在CM的微程序的位置都是固定的,可以在另外設置一個ROM來存儲每個微程序的首地址,並且每個指令操作碼對應的微程序首地址在該ROM存儲的地址為這個指令操作碼,就是說直接把指令操作碼(是一個二進制編碼)當作地址(所有的指令操作碼均不相同)去訪問該ROM就可以快速得到這個指令操作碼所對應微程序在CM中的地址~ 給出下地址的方法

直接給出:當前為A,下地址通常為B,除非當前微程序執行結束,則無條件轉移到B。如執行結束必然要進入中斷,則可以直接給出 增量計數:將uAR賦予自動加1的特點,這樣可以滿足所有的順序微指令,對於分支/跳轉,就需要改進順序控制字段,分為“轉移控制字段BCF”和“轉移地址字段BAF”,若條件滿足則直接用BAF來改寫uAR 斷定法:順序控制字段分為“非測試字段”和“測試字段”

“非測試字段”直接構成下地址的高位 “測試字段”和“非測試字段”以及狀態(時序等)、指令操作碼等等送入“測試網絡”來生成下地址的地位 這樣就支持多路轉移,轉移的路數由“測試字段”的位數決定(n位則有2^n路)